- 上一篇:基于MATLAB的EIT图像重构研究

- 下一篇:生命探测雷达发射组件设计

在国内,随着数字滤波器的进一步发展,在通信信号处理中数字相关器对特定码序列进行相关处理的能力显得十分特别而高效。数字相关器实质上是起到数字匹配滤波器的作用,即对输入流序列进行相关处理,相关运算,最终完成信号的解码,速度而有效地恢复出传送的信息。数字相关器一般包括:输入序列移位寄存器,参考序列移位寄存器,相关运算阵列和相关求和网络。这四个部分相互联系相互作用是实现数字相关器功能的必要条件。在随着集成电路技术飞速发展的今天,数字信号处理的应用范围迅速扩大,FPGA也逐渐登上时代的舞台。它从只能做一些简单逻辑处理发展到今天可以在一些领域取代定制芯片与专用处理器来实现特定功能的地步。并且FPGA的处理能力正在进一步获得提高,有望实现一些大规模的计算,如稀疏矩阵的乘法运算,交通规划问题仿真等。

本文将FPGA与数字相关器相结合,对基于FPGA的数字相关器进行了设计与仿真,初步实现了数字相关器的匹配滤波的功能,并对实验研究结果进行了总结。

1.2 数字相关器的特点与应用

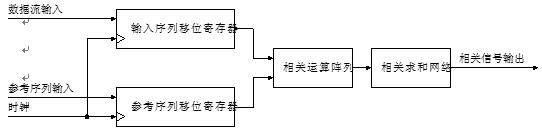

数字相关器一般包括:输入序列移位寄存器、参考序列移位寄存器、相关运算阵列和相关求和网络。它的结构框图如图1.1所示。数字相关器的特点在于它灵活性强、功耗低、易于集成,因此广泛用于帧同步字检测、扩频接收机、误码校正以及模式匹配等领域。数字相关器的工作过程如下:参考序列首先被送入参考序列移位寄存器中,而输入数据流则在时钟驱动下被送入输入序列移位寄存器中。相关运算阵列对输入序列与参考序列之间进行相关运算,然后将相关运算结果送入相关求和网络,由相关求和网络累加求和计算出相关值。

图1.1 数字相关器结构框图

数字相关器普遍应用在通信信号处理中,这个过程实质上是起到数字匹配滤波器的作用,它可对输入数据的码序列进行相关处理,通过相关运算及累加和的方式快速且有效地恢复出传送的信息。高速的数字相关器有着更为广泛的应用:可以用作已知信号的数字卷积器、幅度补偿电路、数字脉冲压缩匹配滤波器、磁控管频率稳定器等。

1.3 本文研究的内容

本文的研究内容是基于FPGA的数字相关器设计,主要采用matlab仿真数字相关器特性,用VHDL语言编写数字相关器FPGA程序,在QuartusII软件环境下完成数字相关器设计,并仿真数字相关器的功能。具体要求如下:

1) 熟悉m序列,应用MATLAB编写长度为31,所有反馈系数的m序列产生程序,绘制自相关函数图和互相关函数图。

2) 设计一数字相关器,其参数如下:输入序列速率100kbit/s, 8位量化精度,本地参考序列,8位量化,采用m序列,长度31,反馈系数为3,5。

3) 应用matlab仿真该数字相关器功能。

4) 应用VHDL语言编写数字相关器程序,在ISE开发环境下仿真实现数字相关器功能。

-

FHA和PHA的交叉验证技术在...

-

HFSS法拉第笼对频率选择表面性能的影响

-

小波分析用于图像增强的研究MATLAB仿真

-

灰色建模技术的通信运行指标预测

-

基于多指标决策的通信网...

-

Verilog的汉明码(15,11)编解码器的设计与仿真

-

AT89C51单片机IIC总线的监控...

上市公司股权结构对经营绩效的影响研究

浅析中国古代宗法制度

g-C3N4光催化剂的制备和光催化性能研究

中国传统元素在游戏角色...

现代简约美式风格在室内家装中的运用

C++最短路径算法研究和程序设计

江苏省某高中学生体质现状的调查研究

巴金《激流三部曲》高觉新的悲剧命运

高警觉工作人群的元情绪...

NFC协议物理层的软件实现+文献综述